はじめに

はじめまして。電気エンジニアのれいです。 今年の4月より新卒として働き始めました。

皆さんもマイコンのADCモジュールを用いてアナログ電圧の値を読み取ることがあると思います。

さて、マイコンのADCを用いて読み取った電圧値、本当に “正しい値” であるかどうかを意識したことはあるでしょうか。また取得した値にノイズが乗っている、値が小さい、などの経験をしたことがある人もいるでしょう。 ADCの精度はADCモジュールそのものの性能に限らず、システム全体の設計、特にADCの使用条件に大きく依存します。

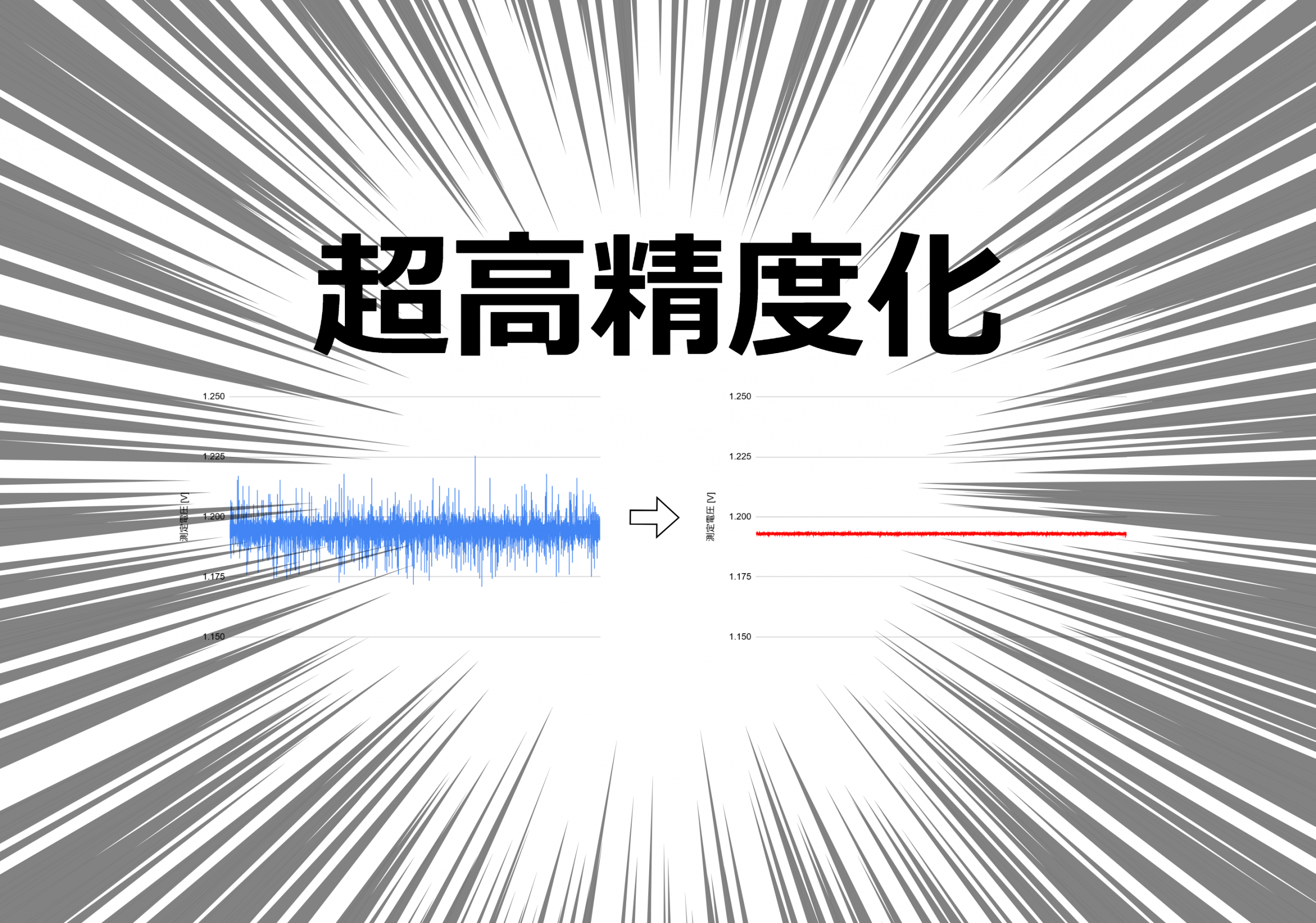

本記事では、ADCでのアナログ測定においてどのような要因が精度低下を引き起こすのか、そして具体的な対策がどの程度精度向上に寄与するのかを検証した結果をご紹介します。

目次

アナログ・デジタル変換(ADC)の動作原理

現在使用されているADCにはいくつか種類があります。

- ΔΣ型

ΔΣ変調とデジタルフィルタを用いてのアナログ値の読み取り。低速度高精度 - 逐次電圧比較(Successive Approximation Register: SAR)型方式

基準電圧に対する二分探索による入力電圧の読み取り。中速度中精度 - パイプライン型

ADCで読み取った値をDACで出力して入力との差分を取り、増幅した電圧を次段のADCで読む、という風にADCの変換を多段ステージ化する方式。高速度低精度 - フラッシュ型

入力電圧を分圧し基準電圧と比較する。超高速度低精度

STM32を含め安価なマイコンに搭載されているADCの多くはSAR型方式を採用しています。この方式ではアナログ入力電圧をデジタル値に変換するプロセスがいくつかのステップを経て実行されます。

- サンプリング: アナログ入力ピンに印加された電圧を内部のサンプリングキャパシタに一定時間チャージし取り込む。このキャパシタに信号を保持する時間を“サンプリング時間”と呼び、サイクル数の設定によって時間を変えられます。

- ホールド: サンプリングされたアナログ電圧をキャパシタに保持したまま、外部入力から切り離す。

- ビット変換: 保持された電圧を基準電圧(VREF+など)と比較しながら、デジタル値に変換していく。これは逐次比較アルゴリズムや二分探索アルゴリズムといったアルゴリズムで行われ(例: VREF+/2と比較、次に残りをVREF+/4と比較…)、変換にかかる時間が“ビット変換時間”とよばれビット数に比例した時間がかかります。

ADCのトータルの変換時間は、サンプリング時間とビット変換時間の和となり、逆数を取ったものがサンプリング周波数となります。特にサンプリング時間は内部のサンプリングキャパシタを充電する時間であり、測定対象の出力インピーダンスが高い場合(例:サーミスタ、RCフィルタ、分圧抵抗など)ではサンプリングキャパシタとRC回路を形成するためサンプリングキャパシタの充電に時間が掛かります。この時定数に対し適切なサンプリング時間が設定がされていないと正確な電圧値が得られなくなります。

最終的なデジタル変換結果は測定精度のビット数を最大値としたアナログ入力電圧と基準電圧の比率で決まります。この変換結果の最も小さな単位は LSB と呼ばれ、N-bitADCの場合、1 LSBの電圧値は以下の式で与えられます。

1 LSB [V] =VREF+ / 2^N (N-bit ADCの場合)

ADCの電圧値は、ADCの測定値にこの1 LSBの電圧値を乗じることで求められます。

V_ADC = VREF+ * ADCvalue / 2^N

実際の測定精度の評価

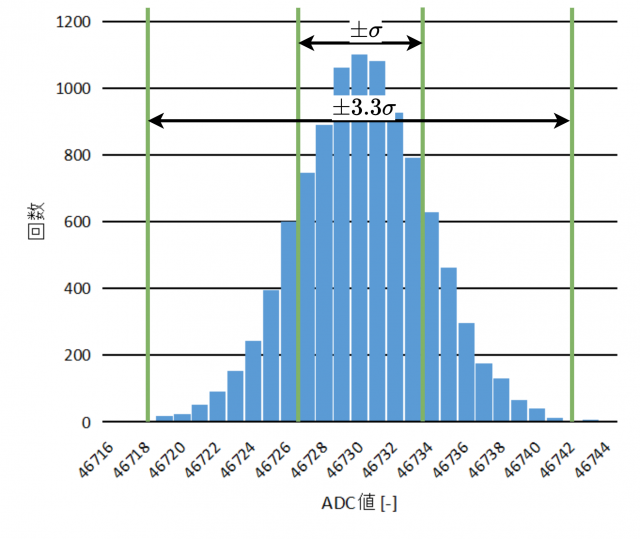

解析のため、ADCの読み取り値のノイズは正規分布に従うと仮定します。殆どの場合でこの仮定は現実と一致します。これを用いてDC電圧(定常状態)測定時のADCの精度の評価が行えます。

DC電圧における測定精度の評価指標の一つとして、実効分解能(Effective Resolution)とノイズフリー分解能(Noise-Free Bits: NFB)が存在します。

実効分解能

理想的なビット数からノイズの影響を実質的に除外した分解能を示す値です。通常、RMSノイズσ [LSB]に基づいて計算され、±1σ (68.3%) の範囲に収まるノイズを考慮した実際の精度を表します。

(Effective Resolution) [bit] = log2((フルスケール値)/2σ)

なお、非常に似た概念として有効ビット数(Effective Number Of Bits: ENOB)というものがあります。実効分解能が直流信号に対する評価なのに対し、ENOBは交流信号のS/N比やTHDから計算される過渡的な分解能となります。今回は直流電圧でのみ評価を行ったため算出はしていません。

ノイズフリー分解能

発生するノイズのピークtoピーク値Vp-pのビット精度を理想的なビット数から差し引いた値で測定可能な精度の最低値を表します。この値は絶対的に測定できる精度の指標となります。

NFB [bit] = log2((フルスケール値)/Vp-p)

また、ピークtoピーク値の他に±3.3σ(99.92%)における値をNFBとする場合もあります。3.3σは分析化学では検出限界値(3σ法)の指標にもなります。

何が原因で誤差は起きるのか

ADCの精度を悪化させる要因は多岐にわたり、これらは大きく分けてADCチップ内部に起因する誤差とADC周辺の環境や回路設計に起因する誤差の2種類に分類できます。

ADCモジュール内部に起因する誤差

事実として、ADCの入力に対する測定値はかなりズレます。

ここでは最小の可能測定範囲(オフセット誤差Eo)、最大の測定範囲(ゲイン誤差Eg)、非線形性誤差(DNL/INL)など様々な誤差が発生します。これらはADCモジュール内部あるいはソフトウェア的な補正を行うことができます。

またADCのビット数による量子化誤差なども精度の低下を招きます。

ADC周辺環境に起因する誤差、精度低下

ADC内部の誤差以上に、外部環境や回路の問題が精度を低下させる大きな要因となります。誤差の原因となる理由を挙げればキリがないですが、その中でも大きな要因を占めるのは以下のような理由です。

- 基準電圧・電源の変動、ノイズ

- アナログ入力信号に直接重畳されるノイズ

- ADCダイナミックレンジと入力信号振幅の不一致

- 線路インピーダンス及び寄生容量の影響

- 温度による影響

- クロストーク、 EMIノイズ

精度・確度向上の方法

このようにモジュール内外に限らず測定精度が悪化する理由は数多く存在します。その中でも比較的容易に対策可能な一例を紹介します。

変換時の電源電圧・基準電圧の把握

ADC基準電圧VREF+の正確な値を知ることが高確度測定には必須です。安定性と精度の高い内部のリファレンス電圧(ADCの基準電圧VREF+ではない)を持っているモジュールではその電圧を読み取り逆算することによりADCの基準電圧VREF+を求めることができます。

STM32ではVrefintという内部のリファレンス電圧を読み取る専用のチャンネルが存在し、また工場出荷時校正がされているため以下の式により高確度なADCの基準電圧VREF+を求めることができます。

VREF+ = (出荷時の基準電圧VREF+の電圧値)(校正値)/(ADCによる内部基準電圧の測定値)

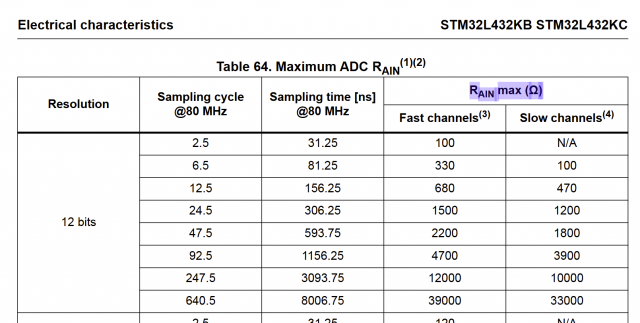

サンプリング時間の適切な設定

先ほど書いた通り、電圧源の出力インピーダンス(および経路上の直列インピーダンス)に対する不適切なサンプリング時間の設定は測定確度の低下を招きます。データシートではサンプリング時間やサンプリング周波数に対する直列インピーダンスの最大値が規定されています。

(https://www.st.com/resource/en/datasheet/stm32l432kc.pdf より引用)

また、キャパシタにより入力端子の交流インピーダンスを下げる(入力端子の電荷量をプールしておく)こともサンプリング時間の短縮に向上に有効です。

ADCのキャリブレーション

STM32L4シリーズのようにADCモジュールで補正(キャリブレーション)機能を有している場合があります。無い場合でも、オフセット誤差とゲイン誤差から線形変換で補正を行えます。

オーバーサンプリング

先程書いた通り、ADCの測定値は正規分布に従います。そのため測定したいサンプリング数に対して数倍高い回数サンプリングを行いその値を変換すること(オーバーサンプリング)により真値に近い平均値を得ることができます。このときの精度上昇は定量的に評価でき、オーバーサンプリングの乗数Nに対し10log10(N)でSNRが向上します。このためオーバーサンプリング数N=4倍でSNR=6dB、つまり雑音比が倍になり実効分解能が1bit増えます。

直列抵抗の追加

直感や一般的な電子工学の常識に反することですが、アナログ線路を数百Ωから数kΩの高い抵抗値にすることは精度向上の観点で非常に有効な場合があります。これはSAR型ADCのサンプルキャパシタと抵抗がRCローパスフィルタ回路を形成し、ノイズの帯域が制限されるため折り返し雑音が減少するためです。測定対象のインピーダンスによる充電時間やサンプリング時間の増加は考慮する必要が出てきます。

実験

これらの情報を元に、測定対象に対して実際にどの程度の誤差が発生するのかを検証しました。

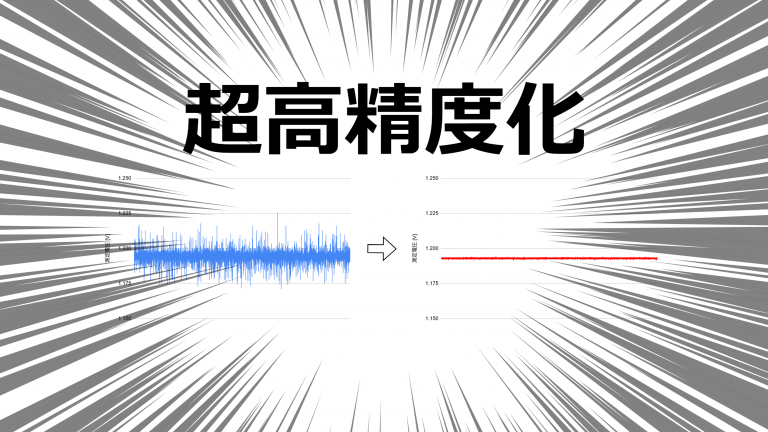

この装置は3つの基準電圧ICを搭載しVp-p<50μVで動作します(思い立って3時間で作りました)。

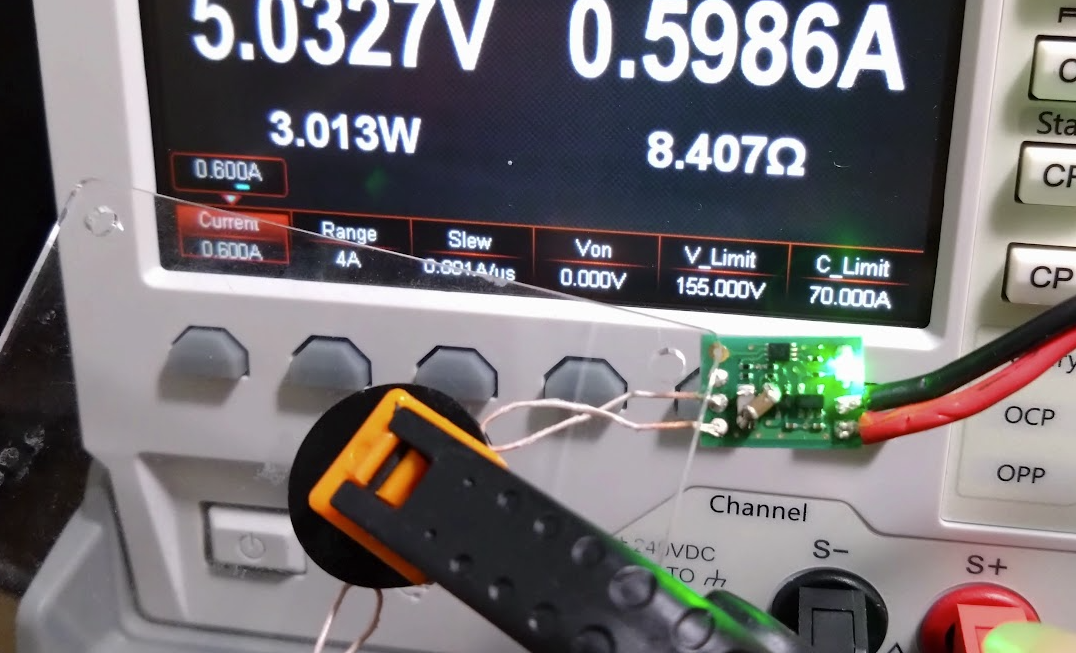

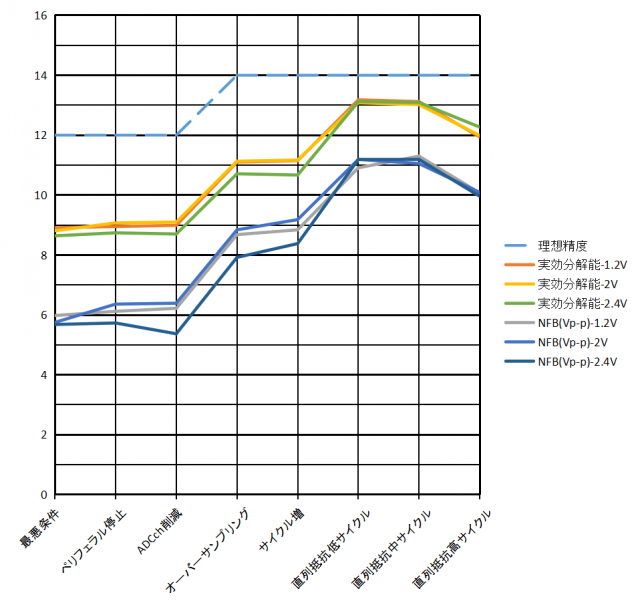

測定環境として、STM32L432KCのタイマモジュールやペリフェラルモジュールを複数個動かし、ADCのクロックは32/6 MHzの2.5cyclesの5ch測定、という悪条件から上記のノイズ対策を段階的に実施し、具体的にどのアプローチが有効なのかの検証を行いました。

AC特性では定常状態で1万サンプルを測定しVp-pと平均値、標準偏差を計算しました。

またDC特性では16bitPWM出力をADC入力にRCフィルタを通して接続し、PWMに対する読み取り電圧を比較し評価を行いました。

測定結果 ― AC特性

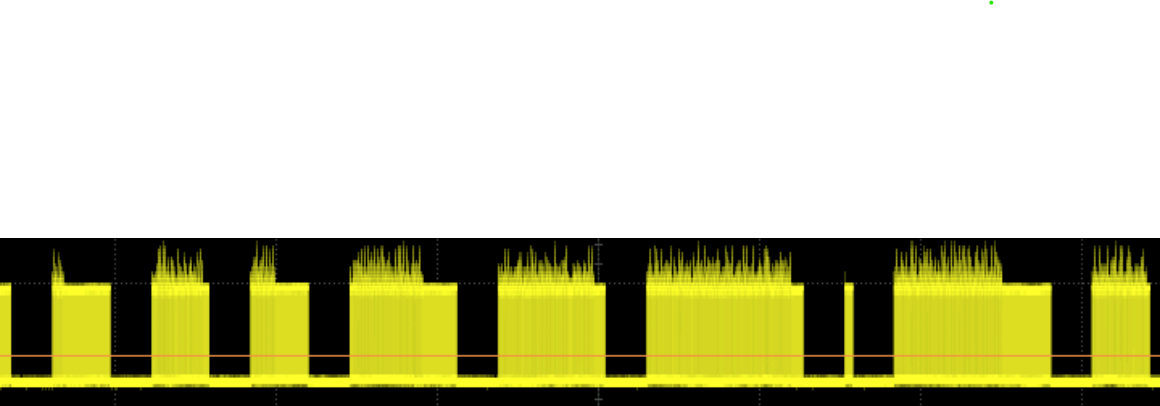

AC特性の測定結果より実効分解能とNFBを計算した結果がこちらです。オーバーサンプリング適用時は理想的な精度が14bit、オーバーサンプリングの都合上値は16bitとして扱っています。

1.2V時測定結果(抜粋)

| 最悪条件 | ペリフェラル停止 | ADCch削減 | オーバーサンプリング | サイクル増 | 直列抵抗低サイクル | 直列抵抗中サイクル | 直列抵抗高サイクル | |

|---|---|---|---|---|---|---|---|---|

| 最大値 | 1459 | 1449 | 1450 | 22819 | 22811 | 22372 | 22759 | 22768 |

| 最小値 | 1394 | 1390 | 1395 | 22659 | 22668 | 22338 | 22733 | 22707 |

| p-p | 65 | 59 | 55 | 160 | 143 | 34 | 26 | 61 |

| 平均 | 1422.30 | 1422.03 | 1421.88 | 22754.22 | 22749.43 | 22357.41 | 22745.43 | 22738.41 |

| 標準偏差σ | 4.25 | 4.15 | 4.03 | 14.89 | 14.44 | 3.53 | 3.69 | 8.34 |

| 理想精度 | 12 | 12 | 12 | 14 | 14 | 14 | 14 | 14 |

| 実効分解能 | 8.91 | 8.95 | 8.99 | 11.10 | 11.15 | 13.18 | 13.12 | 11.94 |

| NFB(p-p) | 5.98 | 6.12 | 6.22 | 8.68 | 8.84 | 10.91 | 11.30 | 10.07 |

この結果より

- 理想精度12bitのADCに対し、外部ノイズ対策やソフトウェアによる最適化を施さない初期状態ではENOBは8.91bit、NFBは5.98bit程度

- ペリフェラル停止、ADCチャンネル削減、16倍オーバーサンプリング適用、サンプリングサイクル延長、直列抵抗の挿入といった対策を段階的に実施した結果、ENOBは最大で13.18bit、NFBは最大で11.19bitまで改善することが確認。特に、オーバーサンプリングと直列抵抗の挿入がそれぞれ約2bitずつの分解能向上に寄与することが顕著

- 直列抵抗挿入時の低サイクルでは平均値の低下が確認

ということが確認できました。

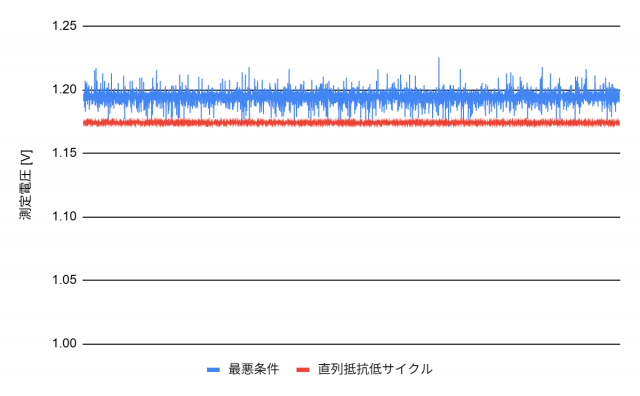

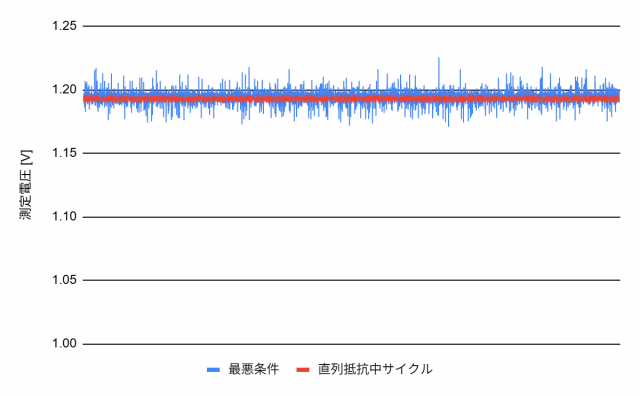

特筆すべきは最悪値と直列抵抗低サイクル、それに対する直列抵抗中サイクルの測定値です。

このときの最悪条件の平均値は1.1944V、直列抵抗低サイクルの平均値は1.1741Vとなっており、理想電圧1.2Vに対し直列抵抗挿入時の低サイクルでの電圧が低くなっていること、それに対し直列抵抗中サイクルでは概ね平均値が一致していることから直列インピーダンスに対して不適切なサンプリング時間の選定は測定確度の低下を招くことも確認できました。

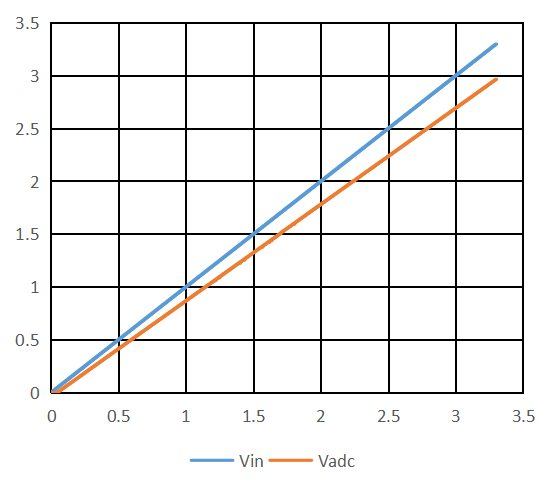

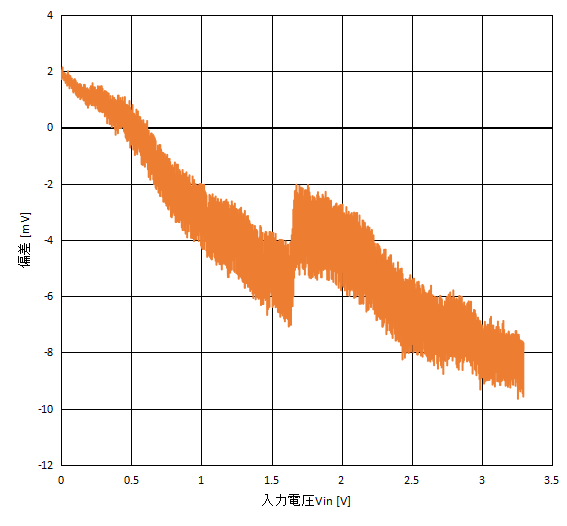

測定結果 ― DC特性

PWMを用いた電圧スイープに対するADC電圧の測定値の偏差が以下の図です(出力電圧と測定電圧の比較図は誤差が極小で グラフ上では重なってしまうため省略しています)。

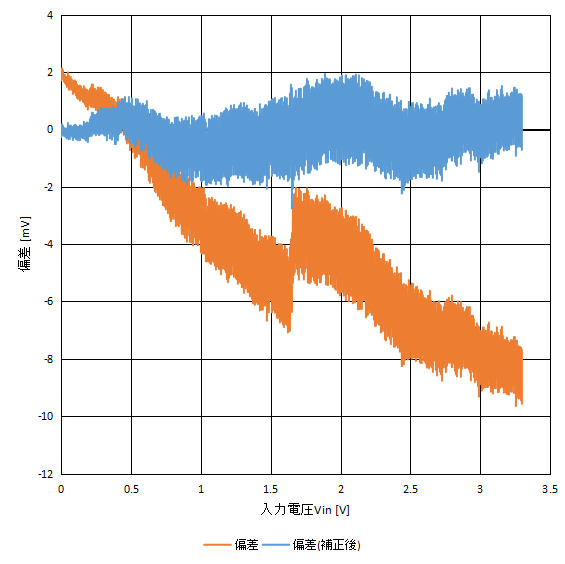

STM32のハードウェア機能として提供されているADCキャリブレーションを実施後のため、この時点でほぼ値が一致しており誤差も10mV程度まで抑えられています。この図から、測定範囲をいくつかの区間に分割しオフセットやゲインを調整した結果以下のようになりました。

このときの各種統計量は以下のようになっており、測定レンジ全体を通して11.1 bitの精度と±2.5mV以下の確度を達成することができました。

| 単位 | 数値 |

|---|---|

| 誤差[mV] | 1.934 ~ -2.754 |

| Vp-p[mV] | 4.688 |

| 偏差の平均[mV] | -0.097 |

| σ[mV] | 0.754 |

| ENOB [bit] | 11.10 |

総評

実際の出力電圧に対するADCの測定値の評価を実施し、無対策時の実質的な精度数の把握、対策を行うことで適切な精度・確度向上が行えることを確認しました。

アナログ信号を高精度に測定するためには単にADCの分解能が高いチップを選ぶだけでは不十分であり、周辺のハードウェア設計、そしてアナログ経路の品質が非常に重要となります。加えて、適切なサンプリング時間の設定やソフトウェアによる信号処理(平均化など)も精度向上に大きく寄与します。

本記事でご紹介したように、ADC一つ取ってもそのままポン付けでは性能をうまく引き出すことができず、また個体差、基板や回路の特性、設計により特性が大きく変わってしまうことがハードウェア設計の難しいところであり改善する余地ともなりえます。 もちろん、要求される精度、必要な変換速度、利用可能なリソース、そして設計コストはトレードオフの関係にあります。アプリケーションの要件をしっかりと把握し、今回ご紹介した様々な手法の中を知っておくこと。なにより、回路を最適化するためにはハードウェアとソフトウェアの両面からのアプローチが不可欠です。両方のレイヤーに造詣を深めておくことが高精度なアナログ測定を実現する上での第一歩となるでしょう。

今回の検証はADC単体の理想的な測定方法によるもので、電圧源の種類やオペアンプ等を用いた変換を用いた場合などでは誤差の要因などが重なるためそのままでは適用できない場合があります。どんな回路にも適用できる一般論という銀の弾は存在しませんが、このような方法を知った上で実基板を用いて評価を実際に行うことが高精度化への近道です。

追記

「ADCの値から電圧に変換するとき、2^Nで割るべきか、2^N – 1で割るべきか」── この話題はよく議論されますが、殆どの場合で2^Nで割るのが正解でしょう。 たとえば数多くのマイコンやADCのICなどではVREF+の電圧で2^N LSBとなるように設計されているため、測定できる最大値(12bitADCなら4095)はVREF+ -1 LSB [V]となります。

参考資料

STM32マイクロコントローラで最高のADC精度を実現する方法 – STMicroelectronics

https://www.st.com/resource/ja/application_note/cd00211314-how-to-optimize-the-adc-accuracy-in-the-stm32-mcus-stmicroelectronics.pdf

ADC12オーバーサンプリングによる高分解能の実現- Texas Instruments

https://www.tij.co.jp/jp/lit/an/jaja088/jaja088.pdf

12 ビット A/D コンバータの変換精度向上方法 – Renesas

https://www.renesas.com/ja/document/apn/rl78g1a-12-ad-rev100

アナログ-デジタルコンバータのノイズ、ENOBおよび有効分解能を理解する – Analog Devices

https://www.analog.com/jp/resources/technical-articles/noise-enob-and-effective-resoluition-in-analog-to-digital-converter-circuits–maxim-integrated.html

アプリケーションの種類に応じ、ADCのアーキテクチャを適切に選択する – Analog Devices

https://www.analog.com/jp/resources/analog-dialogue/articles/the-right-adc-architecture.html

ADCの入力ノイズ:良いノイズと悪いノイズと厄介なノイズ 良いノイズとはノイズ・ゼロのこと? – Analog Devices

https://www.analog.com/jp/resources/analog-dialogue/articles/adc-input-noise.html

今さら聞けないA-D変換の要点 – 日経クロステック(xTECH)

https://xtech.nikkei.com/dm/article/LECTURE/20100514/182586/

上本 道久,分析の信頼性を支えるもの 検出限界と定量下限の考え方,ぶんせき,03862178,東京 : 日本分析化学会,2010-05,2010年,5,216-221, https://cir.nii.ac.jp/crid/1520572358205507072, https://www.jsac.or.jp/bunseki/pdf/bunseki2010/201005nyuumon.pdf